In the fast-paced world of hardware design and verification, ensuring robust and efficient verification processes is paramount. UVM (Universal Verification Methodology) Register Models and PSS (Portable Stimulus Standard) Compiler have become instrumental in achieving this goal. In this article, we'll explore how the integration of UVM Register Models and PSS Compiler is taking hardware verification to new heights.

UVM Register Models: The Foundation

UVM Register Models serve as the backbone of UVM-based verification environments. They offer a structured and systematic way to represent hardware registers within a design, crucial for controlling and monitoring hardware functionality.

These models encompass key elements, including registers, fields, access permissions, and support for operations like read, write, and bit-level modifications. The structured nature of UVM Register Models bridges the gap between the design specification and the verification testbench, ensuring a comprehensive and organized approach to verification.

The Power of UVM Register Models

UVM Register Models come with several compelling benefits:

-

Structured Abstraction: They provide an organized and intuitive representation of registers and their associated fields, simplifying interactions with registers and the creation of complex test scenarios.

-

Reusability: UVM Register Models can be reused across different projects, saving time and effort that would otherwise be spent recreating models for each design.

-

Self-Checking Capabilities: These models include built-in self-checking mechanisms, automating the verification of hardware behavior.

PSS Compiler: Unifying Verification

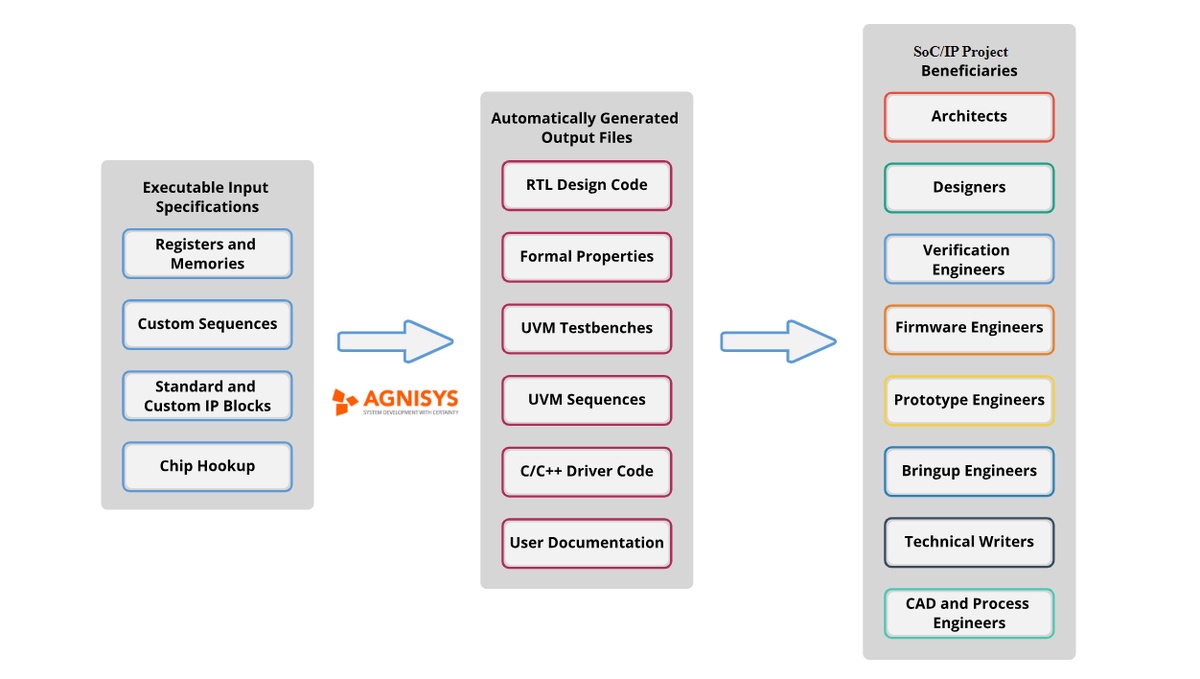

PSS Compiler introduces a standardized approach to defining stimulus scenarios. It offers a high-level method for describing verification scenarios that can be adapted for various verification platforms, such as simulation, emulation, and formal verification. This standardization enhances verification efficiency and encourages the reuse of test scenarios.

By integrating UVM Register Models and PSS Compiler, verification engineers can create intricate test scenarios that encompass both functional operations and interactions with registers. This alignment ensures that the verification environment closely mirrors the design specification, reducing the risk of missing critical test scenarios.

UVM Testbenches in Action

UVM testbenches play a pivotal role in hardware verification. They generate stimuli, verify responses, and offer a comprehensive view of the design's behavior. When integrated with UVM Register Models and PSS Compiler, testbenches become more powerful.

UVM Register Models provide a straightforward interface for interacting with registers, enabling testbench components to access and manipulate register values seamlessly. This streamlines the creation of test sequences and ensures that the verification environment accurately reflects the design's register structure.

Real-World Application

To illustrate the power of UVM Register Models and PSS Compiler, let's consider a practical example. Imagine a hardware design featuring a configuration register that controls various operating modes. Using a UVM Register Model, you can define this register's fields, their access attributes, and default values. The PSS Compiler can then generate test scenarios that cover all potential combinations of field settings, ensuring comprehensive verification of the register's functionality.

UVM Register Sequences: Precision and Control

UVM Register Sequences offer a systematic way to define sequences of register transactions. With UVM Register Models and PSS Compiler, you can create sequences that precisely target specific registers and their associated fields. This level of control guarantees that no aspect of the design is left unverified.

In conclusion, the integration of UVM Register Models and PSS Compiler is a transformative approach in hardware verification. By providing structured methods for modeling registers and generating high-level test scenarios, these tools significantly enhance verification efficiency and accuracy. Incorporating them into your UVM testbench can lead to more robust and comprehensive verification, reducing the risk of hardware defects and ensuring that your design performs precisely as intended. In the ever-evolving field of hardware engineering, this integration is a vital step towards mastering hardware verification.

No comments yet