In the intricate tapestry of modern hardware design, the trio of IP-XACT, SystemRDL, and UVM Register Models forms the backbone of a robust and efficient development process. This article aims to demystify the roles of each component, shedding light on their interactions and the seamless integration that drives innovation in contemporary hardware design.

IP-XACT: Standardization for Interoperability

At the heart of hardware interoperability lies IP-XACT, a standard designed to bring harmony to intellectual property descriptions. Through its XML schema, IP-XACT provides a universal language for packaging and configuring IP blocks. By fostering standardization, IP-XACT ensures that IP components seamlessly integrate into different design environments, reducing development time and enhancing overall project efficiency.

SystemRDL: Precision in Register Description

SystemRDL emerges as a beacon of precision in the intricate process of specifying registers and their configurations. This high-level language serves as a bridge between design intent and verification, offering a structured syntax for articulating intricate register hierarchies and properties. SystemRDL empowers designers to express their vision with clarity, laying the foundation for a seamless transition from concept to implementation.

UVM Register Models: Bridging the Verification Divide

UVM Register Models play a crucial role in the verification landscape, acting as a bridge between design and verification teams. The UVM Register Layer, a standardized interface, facilitates clear communication between the components, ensuring that register functionality is accurately and efficiently verified. This abstraction simplifies the verification process, fostering collaboration and reducing the likelihood of discrepancies between design and verification representations.

UVM Model Generation: Accelerating Verification Setup

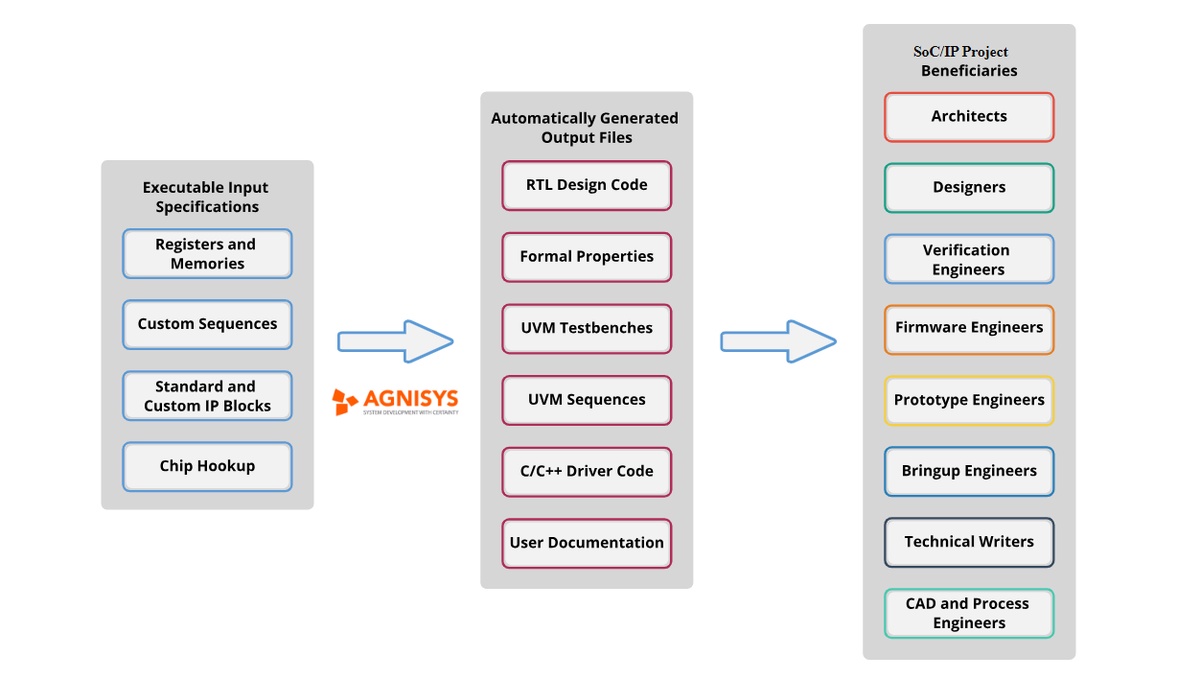

UVM Model Generation introduces an automation layer to the verification process, accelerating the translation of high-level specifications, often in SystemRDL, into UVM Register Models. This automated generation not only expedites the verification setup but also guarantees consistency between design and verification representations. It becomes a cornerstone for maintaining accuracy and reducing the risk of errors in the verification environment.

Register Model Generator: Crafting a Seamless Translation

In the intricate dance of hardware design, the Register Model Generator takes center stage. It is the tool that crafts a seamless translation of register specifications, particularly those articulated in SystemRDL, into UVM Register Models. This automated translation ensures that the UVM Register Models faithfully represent the intended register behavior, establishing a cohesive link between the design and verification domains.

PSS Compiler: Embracing Portable Stimulus

The PSS Compiler introduces a new era in verification methodologies by embracing the Portable Stimulus Standard (PSS). This standard allows engineers to create abstract, portable stimulus descriptions that transcend specific verification platforms. The PSS Compiler transforms these abstract descriptions into executable testbenches, streamlining the verification process and enhancing test scenario reusability across diverse environments.

Conclusion: Orchestrating Harmony in Hardware Design

In the symphony of modern hardware design, the harmonious interplay between IP-XACT, SystemRDL, and UVM Register Models orchestrates efficiency and innovation. Standardization, precision, automation, and abstraction are the pillars supporting a streamlined development process. As hardware design evolves, engineers equipped with a profound understanding of these tools are better positioned to navigate the complexities and drive progress in the ever-evolving landscape of contemporary hardware development. Embrace the synergy of IP-XACT, SystemRDL, and UVM Register Models to decode the DNA of modern hardware design and pave the way for groundbreaking innovations.

No comments yet