Introduction: In the intricate dance of ASIC design, excellence is not just a goal—it's an imperative pursuit. The Universal Verification Methodology (UVM) and its Register Abstraction Layer (RAL) stand as architectural pillars, guiding the industry toward precision and efficiency. This exploration dives deep into the art and science of implementing automated UVM RAL, spotlighting the UVM Register model, and drawing inspiration from real-world UVM showcases that vividly illustrate the transformative impact of automation.

Unraveling the UVM Register Abstraction Layer (RAL): The UVM RAL serves as a vital bridge between design and verification, providing a standardized interface for meticulous register control. By abstracting the intricacies of register implementations, the UVM RAL not only simplifies the verification process but also ensures a consistent approach crucial for the success of ASIC designs.

Automation: Merging Art and Science: Automation within the UVM RAL framework is both an art and a science. It liberates designers from manual efforts, minimizing the risk of human errors that could impede the verification process. This strategic automation extends to establishing uniformity across the design, aligning the verification environment seamlessly with the register specifications. In the complex landscape of ASIC designs, characterized by numerous registers demanding thorough validation, automation becomes the fusion of artful precision and scientific efficiency.

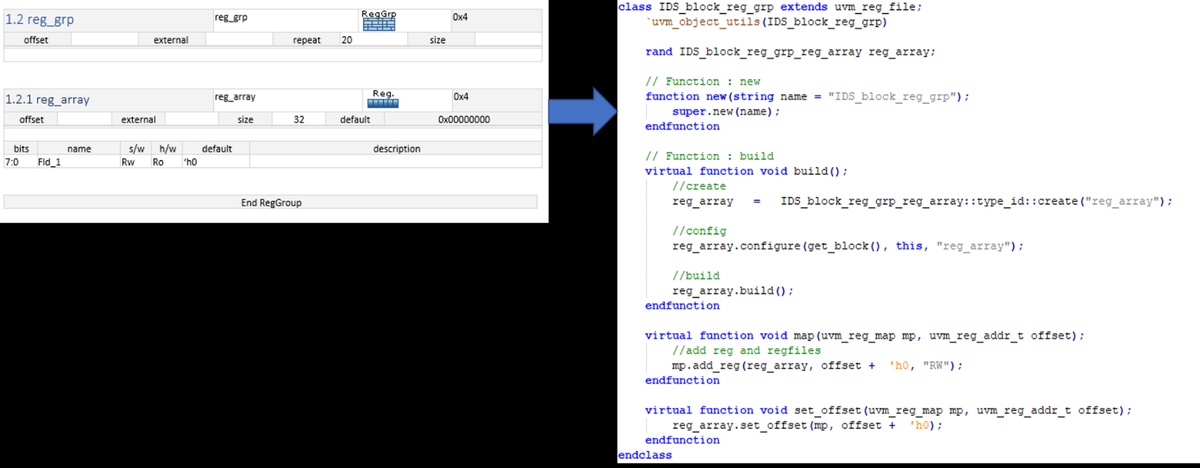

Elegance of the UVM Register Model: At the heart of the UVM RAL lies the UVM Register model—an elegant representation of register behavior and properties. Automating the UVM Register model involves its generation from a register description language, showcasing a seamless integration process enriched by collaboration with IP-XACT.

Harmonious Symphony with IP-XACT: IP-XACT, with its standardized XML format, plays a pivotal role in seamlessly integrating UVM Register models with register descriptions. This integration simplifies the specification process and fosters collaboration between design and verification teams. A unified register description ensures a smooth flow of consistency from design to verification, elevating the coherence of the entire project.

Meticulously Orchestrated Automated Workflow: The automated workflow for UVM RAL unfolds with meticulous orchestration. The register description is captured in IP-XACT, defining registers, fields, and properties with precision. Subsequently, an automated tool translates this IP-XACT description into the UVM Register model, ensuring that any modifications in register specifications seamlessly propagate to the verification environment.

The UVM Register model becomes the linchpin for the UVM RAL. Automation extends to the generation of UVM sequences and testbenches, leveraging the UVM Register model to expedite the creation of comprehensive verification environments. Now, let's immerse ourselves in real-world UVM showcases to witness the artistic and scientific impact of this holistic automation approach.

UVM Showcases: A Tapestry of Excellence: Imagine a scenario where an ASIC design encompasses diverse IP blocks, each with distinct register specifications. UVM showcases offer a vibrant tapestry of how automation tools adapt to these diversities, showcasing precision, flexibility, and customization in action. These showcases provide a living canvas, illustrating the dynamic nature of UVM Register model automation in addressing real-world design complexities.

Strategic Solutions for Challenges: While automation is a potent tool, addressing challenges strategically is imperative. Diverse register specifications across different IP blocks demand customization and flexibility in automation tools. Robust error-handling mechanisms become vital to detect and rectify discrepancies between the IP-XACT description and the generated UVM Register model.

Conclusion: Automating the UVM Register Abstraction Layer is not just a process; it's a symphony of art and science in the ever-evolving landscape of ASIC design. The integration of UVM Register models with IP-XACT, coupled with real-world UVM showcases, not only accelerates the verification process but also elevates the overall quality of ASIC designs. As the semiconductor industry propels forward, embracing these artistically and scientifically orchestrated automation methodologies becomes paramount for staying at the forefront of innovation and ensuring the resilience of ASIC products in an ever-evolving market.

No comments yet