Introduction:

In the ever-evolving domain of hardware verification, the Universal Verification Methodology (UVM) Register Layer stands as a key enabler, providing a structured framework for modeling and verifying registers. This article takes a comprehensive dive into the strategies and methodologies employed by the UVM Register Layer, unraveling its core components, exploring advanced techniques, and shedding light on how it serves as the linchpin for achieving mastery in hardware verification.

UVM Register: Unveiling the Core Element:

At the core of hardware designs lies a tapestry of registers, embodying the intricacies of configuration settings and operational parameters. UVM Register, as the elemental abstraction, introduces a systematic approach to capturing and interacting with these registers during the verification process. Each UVM Register serves as a virtual representation, encapsulating properties and behaviors that streamline the translation of design intent into verification scenarios.

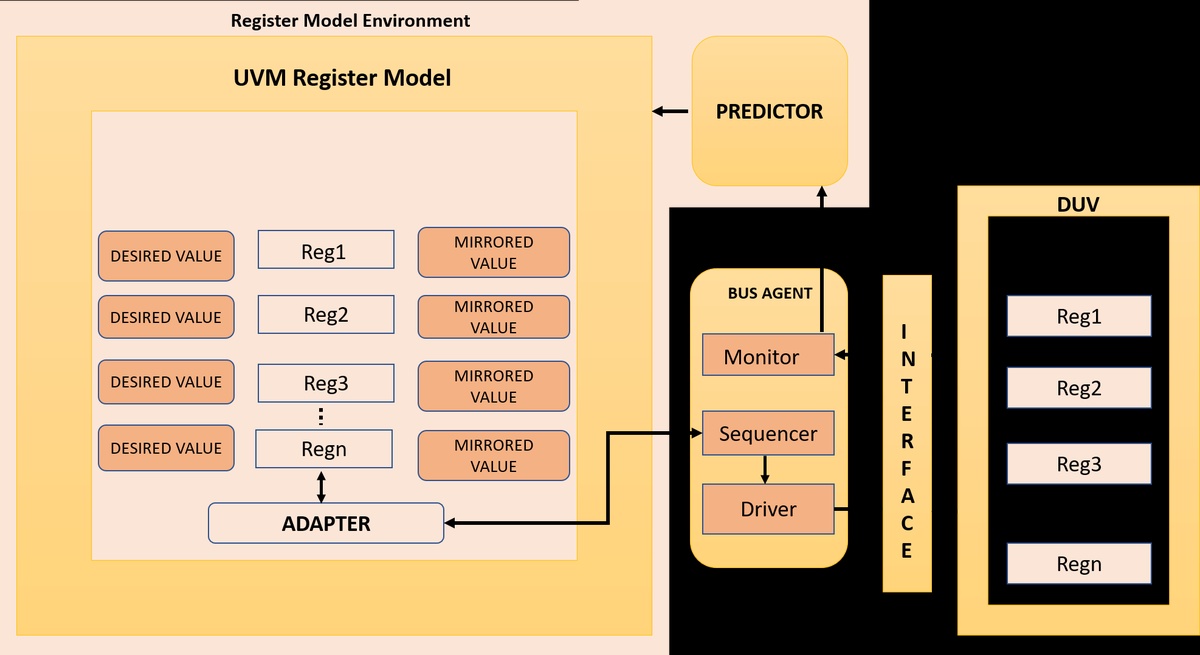

UVM Register Model: Architectural Elegance in Verification:

The UVM Register Model elevates the abstraction of individual registers to an architectural level, creating a unified representation that mirrors the hierarchical structure of the design. It encapsulates registers, defines intricate fields within registers, and organizes them into logical RegBlocks. This model acts as a cornerstone for verification, fostering clarity, modularity, and a seamless translation of the design's hierarchical intricacies into a verification-friendly environment.

Key Components of UVM Register Model:

-

Registers:

- Attributes: Address, data width, access policies, and reset values.

- Role: Fundamental representations of hardware registers.

-

Fields:

- Attributes: Position, width, access permissions, and reset values.

- Role: Defines specific bit fields within registers.

-

RegBlocks:

- Attributes: Hierarchical organization, promoting modularity.

- Role: Logical grouping of related registers.

UVM Register Layer: Strategies for Verification Excellence:

-

Transaction Sequences:

- Develop transaction sequences that emulate real-world scenarios of register access. This strategy ensures a comprehensive verification of register functionality, covering diverse access patterns and corner cases.

-

Callback Customization:

- Leverage the extensibility provided by UVM Register Layer through callbacks and hooks. Customize these callbacks to tailor the verification environment, enabling verification engineers to inject intelligence and adaptability into the verification flow.

-

Intelligent Configurability:

- Implement dynamic configurability features within the UVM Register Layer. This allows verification engineers to dynamically control register behavior during runtime, adapting the verification environment to evolving test scenarios without the need for extensive code modifications.

Advanced Techniques for UVM Register Layer Mastery:

-

Predictive Modeling:

- Explore predictive modeling techniques where the UVM Register Layer anticipates potential register interactions. This proactive approach enhances the efficiency of the verification environment by predicting and addressing potential issues before they occur.

-

Parallel Transaction Execution:

- Implement parallel execution of register transactions to simulate real-world scenarios where multiple registers are accessed simultaneously. This technique enhances the realism of the verification environment and ensures the robustness of the design under complex access patterns.

-

Integration with Formal Verification:

- Integrate the UVM Register Layer seamlessly with formal verification tools. This synergistic approach combines the strengths of simulation-based verification with formal verification, providing a more exhaustive and thorough verification of register functionality.

Conclusion: Ushering in a New Era of Verification Mastery:

In conclusion, the UVM Register Layer is not merely a tool but a strategic framework that, when mastered, unlocks unparalleled efficiency and precision in hardware verification. As the complexities of modern digital designs continue to surge, adopting advanced strategies within the UVM Register Layer becomes imperative. By employing intelligent transaction sequences, customizing callbacks, and embracing dynamic configurability, verification engineers can navigate the intricate landscape of hardware verification with finesse and achieve a mastery that transcends conventional boundaries. The UVM Register Layer, with its depth and flexibility, stands as a beacon guiding the way to a new era of verification excellence in the dynamic realm of hardware design.

No comments yet