In the ever-evolving landscape of System-on-Chip (SoC) design and verification, the Universal Verification Methodology (UVM) Register emerges as a critical cornerstone, orchestrating a symphony of precision and reliability in the intricate dance between design and verification components. This article embarks on a comprehensive journey through the essential elements of UVM Register, delving into the hierarchical tapestry of the UVM Register Model, and ultimately revealing the transformative influence of the Register Model Generator. Together, these elements propel the industry towards a new era of intelligent design automation.

UVM Register: Architecting Verification Excellence

At the nucleus of SoC verification, the UVM Register plays an indispensable role. It functions as the silent architect, defining the rules that govern the behavior of hardware registers within the SoC. By establishing a standardized interface, it ensures a seamless communication bridge between the intricate design intricacies and the rigorous verification process, setting the stage for meticulous validation and reliability.

Decoding Complexity: UVM Register Model as a Hierarchical Guide

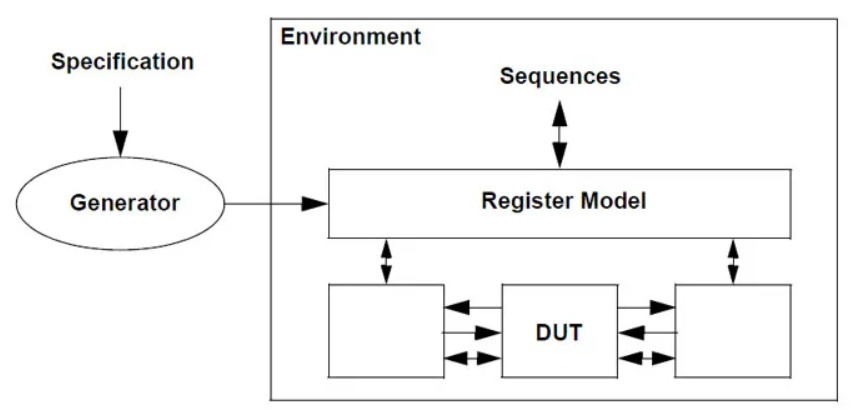

Building upon the foundation laid by UVM Register, the UVM Register Model introduces a sophisticated hierarchical structure. This model not only simplifies the verification process but also acts as a navigational guide through the intricate organization of registers within the SoC. It provides a modular and scalable framework, allowing verification teams to dissect and validate complex designs with a level of efficiency and adaptability that is paramount in the contemporary landscape of chip development.

The Rise of Automation: Register Model Generator's Pioneering Role

In the pursuit of heightened efficiency and accuracy, the Register Model Generator emerges as a revolutionary force. This cutting-edge tool redefines the paradigm of design automation by introducing a range of transformative advantages that propel the industry towards a future where intelligent automation becomes the bedrock of SoC design and verification.

Accelerating Time-to-Verification

The Register Model Generator stands as a catalyst in expediting the creation of UVM Register Models, significantly reducing manual efforts and expediting time-to-verification. Its efficiency becomes a pivotal asset, allowing verification teams to navigate the complexities of modern chip designs with agility, meeting project timelines without compromising the thoroughness of the verification process.

Precision Amplified through Automated Consistency

Automation with the Register Model Generator minimizes the risk of inconsistencies, ensuring that the generated Register Models align seamlessly with the design specifications. This precision not only amplifies the reliability of verification results but becomes a cornerstone for ensuring the quality and integrity of modern SoC designs in the face of increasing complexity.

Unleashing Reusability Across Project Horizons

The Register Model Generator seamlessly enables teams to leverage and reuse models across a spectrum of projects. This not only optimizes resources but becomes a driving force in establishing a standardized framework for UVM Register Models. The result is a culture of collaboration and knowledge transfer that extends beyond individual project boundaries, fostering efficiency and consistency across diverse endeavors.

Seamless Integration for Workflow Synchrony

The Register Model Generator seamlessly integrates into established design and verification workflows, ensuring a harmonious adoption process. Its compatibility with existing frameworks allows design and verification teams to embrace the tool effortlessly, enhancing overall workflow efficiency and promoting a cohesive approach to intelligent design automation.

Paving the Way: Intelligent Design Automation in Focus

In conclusion, the triumvirate of UVM Register, UVM Register Model, and the Register Model Generator marks a transformative journey towards intelligent design automation in SoC verification. As the industry grapples with the intricacies of modern chip designs, the Register Model Generator stands as a dynamic catalyst, steering the course towards a future where complexity is not just navigated but harnessed with precision, efficiency, and the transformative power of intelligent automation. This marks a paradigm shift, where the fusion of human expertise and cutting-edge tools propels the SoC design and verification landscape into uncharted territories of innovation and efficiency,

No comments yet