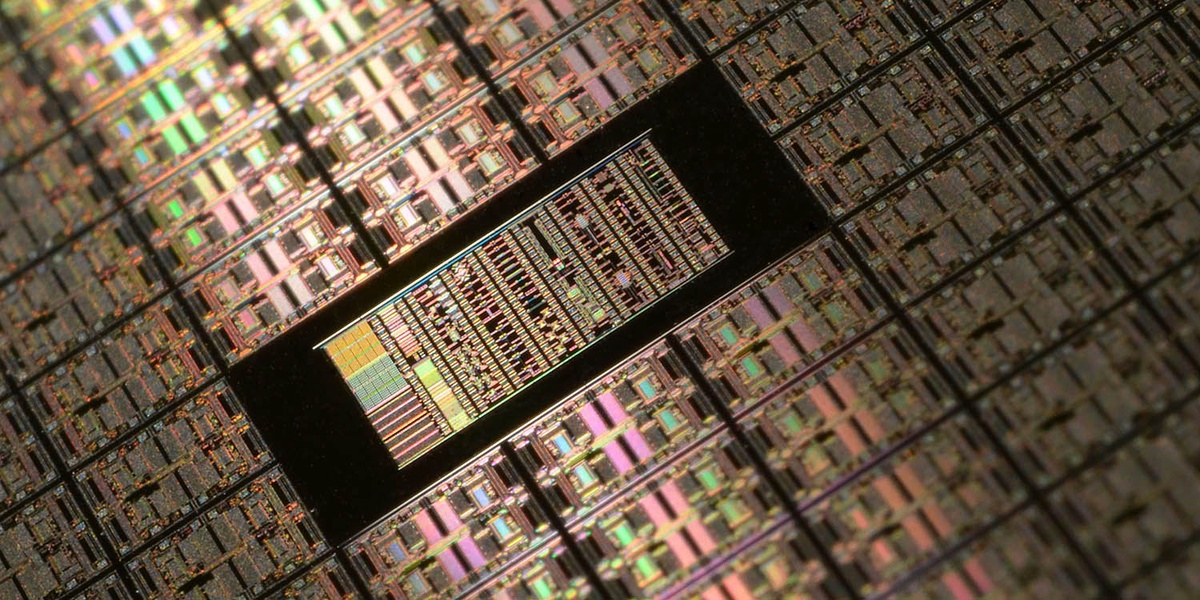

The race to produce ever-smaller, more efficient computer chips is well underway, with chipmakers TSMC and Samsung already producing 5nm devices in high-volume production. TSMC has even set its sights on producing 3nm silicon by the end of the year. However, these ambitious goals come with significant challenges that must be addressed to meet them.

The Challenge of EUV Stochastic Defects

One of the biggest challenges facing chipmakers today is the need to identify defects and ramp manufacturing yield faster than ever before. This is particularly important in the case of extreme ultraviolet (EUV) lithography, which is used to create the smallest features on modern computer chips. EUV lithography allows for the creation of patterns with feature sizes as small as 7nm, but it also introduces new types of defects that must be managed.

One such defect is the EUV stochastic defect, which is a non-repeating patterning defect that can occur at random locations on a chip. These defects can take many forms, including microbridges, broken lines, or missing contacts. They are particularly difficult to manage because they are not easily predictable, and they can occur randomly throughout the production process.

Strategies for Controlling Stochastic Variation

To address these stochastic defects, engineers require high-throughput inspection strategies and Zero Defect tools semiconductors that can quickly and accurately identify defects as they occur. Traditional inspection techniques, such as optical inspection or electron microscopy, are too slow and too expensive to be used on a large scale. Instead, chipmakers are turning to new techniques such as inline metrology and machine learning algorithms to identify and classify defects in real time.

Another critical challenge facing chipmakers is the need to address stochastic variation. Stochastic variation can cause a range of problems, including micro bridging, locally broken lines, and missing or merging contacts. These defects can occur randomly throughout the production process and can be difficult to predict and manage.

Importance of Real-Time Defect Analysis

To control these defects to a level deemed acceptable for high-volume production, chip manufacturers must resolve sources of systemic variation. This involves identifying and addressing the root causes analysis in semiconductors in the production process, such as variations in material properties or process parameters.

One promising approach to addressing stochastic variation is the use of statistical process control (SPC) techniques. SPC involves monitoring key process parameters in real time and using statistical analysis to identify trends and patterns that could lead to defects. By identifying these trends early, engineers can take corrective action before defects occur, reducing the need for time-consuming and costly rework.

Importance of Process Control and Monitoring

In addition to addressing stochastic defects and variation, chipmakers are also exploring new materials and structures to improve the performance of their chips. For example, some chipmakers are experimenting with new materials such as gallium nitride (GaN) and silicon carbide (SiC) to improve the efficiency and power handling capabilities of their chips.

Other chipmakers are exploring new device structures such as finFETs and nanowires to improve the performance and reduce the power consumption of their chips. These new structures are more complex than traditional planar devices, and they require new manufacturing processes and inspection techniques to ensure their quality and reliability.

Conclusion

In conclusion, the race to produce ever-smaller, more efficient silicon chips is driving chipmakers to push the limits of what is technologically possible. However, this drive comes with significant challenges that must be addressed to meet these ambitious goals. From identifying and managing stochastic defects to addressing sources of systemic variation, chipmakers must leverage the latest technologies and techniques to stay ahead of the curve. With the right approach, they can continue to deliver high-quality, high-performance chips that power the modern world.

No comments yet